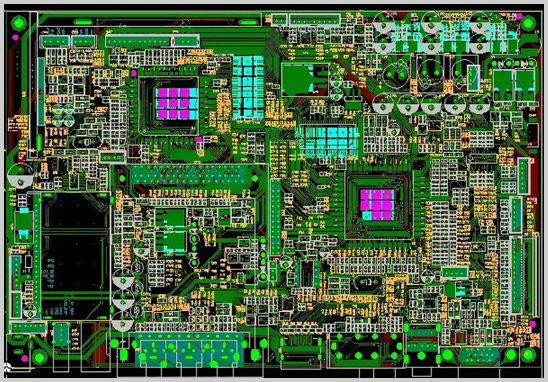

對于從事高速電子設計的工程師來說,信號完整性(SI)是繞不開的話題。高速信號是指信號上升沿時間小于傳輸線傳播時間4倍的信號,其電磁特性使得傳統低速PCB布線策略不再適用。

作為專業高速PCB設計公司,深圳宏力捷電子結合工程實戰經驗,為您整理高速PCB布線的關鍵規則與設計要點,幫助減少EMI問題、提升信號質量與產品可靠性。

高速PCB信號走線9大核心規則

01 屏蔽規則

高速時鐘線、敏感時序線需地線屏蔽。

建議:每1000mil加一含地通孔,構建良好參考回路,抑制EMI耦合。

> 未屏蔽或局部屏蔽可能產生電磁泄漏與串擾。

02 閉環規則

避免高速線形成閉環路徑,否則會產生“環形天線”,放大EMI輻射。

原則:高速線不可圍繞形成閉環

03 開環規則

與閉環相反,高速走線斷開形成開口,也會產生“線形天線”。

避免信號回流路徑中斷

04 特性阻抗連續規則

高速線過孔/跨層必須保持阻抗連續,否則會造成反射與輻射增加。

- 同層線寬一致

- 層間盲埋孔/微盲孔結構合理設計

- BGA封裝過孔補償

05 層間布線方向

相鄰布線層方向應垂直,避免平行引入串擾。

推薦:橫平豎直交替;

不推薦:平行走線相鄰層。

06 拓撲結構規則

多負載高速網絡推薦星型拓撲而非菊花鏈,避免反射與時序偏差。

- DDR、PCIe、SerDes等常用T-branch / Fly-by結構

07 諧振規則

布線長度避免為波長1/4倍數,防止諧振輻射。

08 去耦/旁路電容布局

高速系統必須提供最短回流路徑。

原則:靠近電源引腳,環路面積最小

09 退耦電容放置規則

電容離供電引腳越近越好,優先考慮:

- 小封裝

- 短回流路徑

- 多級容值搭配(0.1uF + 1uF + 10uF)

|

項目 |

建議 |

|

差分線 |

同長、等距、阻抗控制、走線對稱 |

|

時鐘線 |

短、直、屏蔽、遠離干擾源 |

|

參考地 |

大面積地層、連續參考面 |

|

過孔 |

盡量少跳層,差分對同步過孔 |

|

BGA布線 |

微盲孔、HDI結構推薦 |

為什么選擇深圳宏力捷電子進行高速PCB設計?

- 20+年高速PCB設計經驗

- 支持多層、高速BGA、盲埋孔HDI

- 原理圖→布局走線→仿真→BOM→打樣→PCBA量產

- SI、PI、EMC設計能力成熟

客戶只需提供原理圖,其余交給我們。

高速PCB設計不是“堆料”,而是系統設計能力與工程經驗的集合。

遵循上述規則,可顯著提升信號完整性、EMC能力和產品穩定性。

如需專業高速PCB設計咨詢、代工服務,歡迎聯系深圳宏力捷電子。

深圳宏力捷推薦服務:PCB設計打樣 | PCB抄板打樣 | PCB打樣&批量生產 | PCBA代工代料